# DATA SHEET

SP6552FL

同步整流芯片

版本号: V1.0

#### 一、概述

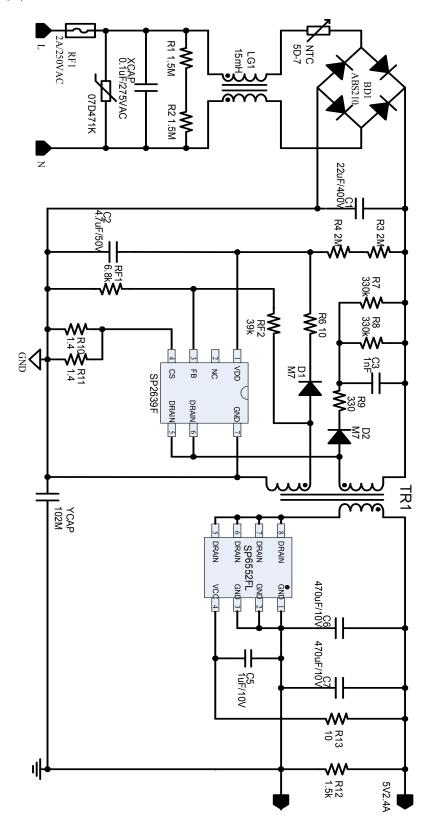

SP6552FL是一颗应用于隔离反激电源系统的次级同步整流芯片。通过模拟次级肖特基整流二极管的工作并以极低的导通电阻来减小损耗。SP6552FL可以工作在断续模式(DCM)和准谐振模式(QR》使用先进的消隐技术使得芯片在各种工作模式下可以稳定可靠地工作。

SP6552FL 检测内置 MOSFET 的导通电阻(Rds-on)上的压降,来控制 MOSFET 的开关。应用外围简单。固定用于 5V 输出的应用方案。

## 二、特点

- 内置 13mΩ/ 45V 功率 NMOS 管

- 极低的静态电流

- 最高工作频率可达 70kHz

- 驱动管脚阻抗下拉电阻 1.2 Ω, 上拉电阻 3.0 Ω

- 50ns 关断延迟时间

- VCC 工作电压范围 3.5V~5.5V

- VCC 过压保护

- 逐周期最小导通时间检测防止误触发

- 工作在断续模式(DCM)和准谐振模式(QR)

- SOP-8 无铅封装

## 三、产品信息

| 产品型号     | 封装       |  |  |

|----------|----------|--|--|

| SP6552FL | SOP-8,无铅 |  |  |

## 四、应用范围

- 5V AC/DC 电源适配器

- 电池充电器

- 数码相机充电器

## 五、极限参数

| 符号                   | 描述            | 范围              | 单位 |

|----------------------|---------------|-----------------|----|

| DRAIN                | 功率管 DRAIN 端电压 | -1~45           | V  |

| VCC                  | VCC 极限电压      | -0.3~6.5        | V  |

| $T_{J}$              | 工作结温          | -40~125         | °C |

| T <sub>STORAGE</sub> | 存储温度范围        | <b>-</b> 55∼150 | °C |

| $T_{LEAD}$           | 焊接温度(锡焊,10秒)  | 260             | °C |

注:如果器件工作条件超出上述各项极限值,可能对器件造成永久性损坏。上述参数仅仅是工作条件的极限值,不建议器件工作在推荐条件以外的情况。器件长时间工作在极限工作条件下,其可靠性及寿命可能受到影响。

## 六、封装热损率

| 产品封装  | θ <sub>JC</sub> (°C/W) | θ <sub>JA</sub> (°C/W) |  |

|-------|------------------------|------------------------|--|

| SOP-8 | 50                     | 130                    |  |

## 七、推荐工作条件:

| 符号    | 描述            | 范围      | 单位  |

|-------|---------------|---------|-----|

| VCC   | VCC 脚电压       | 5       | V   |

| Fsw   | 工作频率          | <70     | kHz |

| DRAIN | 功率管 DRAIN 端电压 | -0.6~40 | V   |

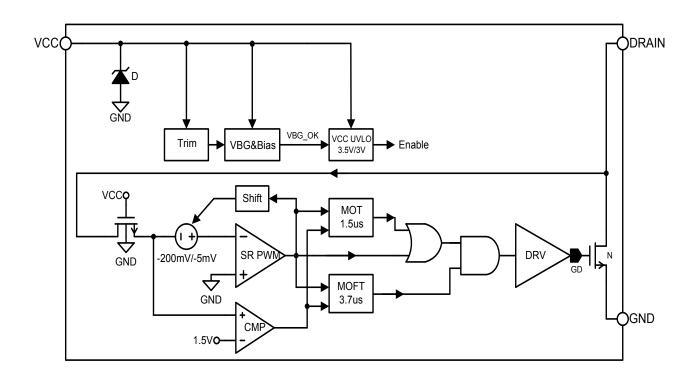

## 八、IC 内部框图

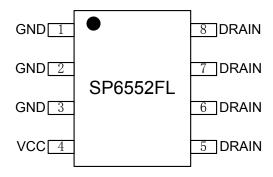

# 九、管脚定义图

| 序号         | 名称    | 功能                   |

|------------|-------|----------------------|

| 1, 2, 3    | GND   | 功率地,连接到内置 MOSFET 的源端 |

| 4          | VCC   | 电源脚                  |

| 5, 6, 7, 8 | DRAIN | 内置 MOSFET 的漏端        |

# 十、电气参数

(除非特别说明,测试条件是:环境温度  $T_A$ =25℃, $V_{CC}$ =5V。有特别说明除外。

| 符号                   | 描述            | <br>  <b>条件</b>         | 范围  |      |     | 単位  |  |

|----------------------|---------------|-------------------------|-----|------|-----|-----|--|

| ,,,,                 |               |                         | 最小  | 典型   | 最大  |     |  |

| VCC 部分               | ·             |                         |     |      | •   |     |  |

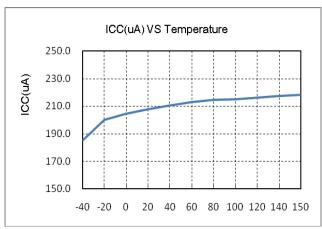

| ICC                  | 静态电流          |                         |     | 200  | 250 | uA  |  |

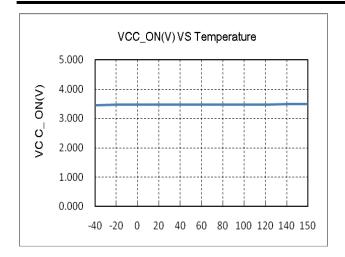

| V <sub>CC_ON</sub>   | 开启电压          | VCC 电压上升                | 3.4 | 3.5  | 3.6 | V   |  |

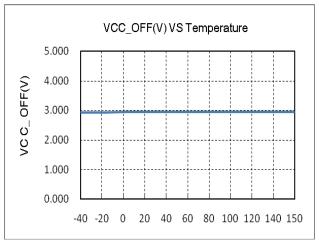

| $V_{CC\_OFF}$        | 关断电压          | VCC 电压下降                | 2.9 | 3    | 3.1 | V   |  |

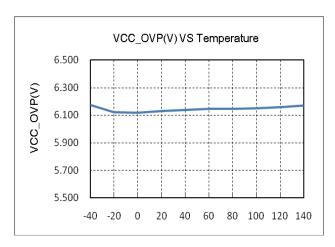

| $V_{\text{CC\_OVP}}$ | 过压保护          |                         | 6   | 6.2  | 6.5 | V   |  |

| 内部 SR 部分             | •             |                         |     |      | •   |     |  |

| MOT                  | 最小导通时间        |                         |     | 1.5  | 2   | us  |  |

| MOFT                 | 最小关断时间        |                         |     | 3.7  |     | us  |  |

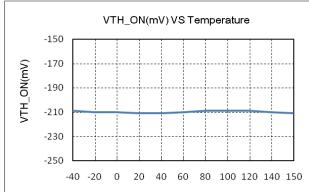

| V <sub>THON</sub>    | SR 开启阈值       | SR 电压下降                 |     | -200 |     | mV  |  |

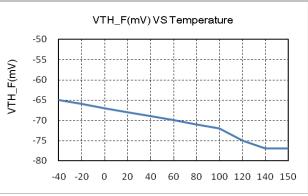

| V <sub>TH_F</sub>    | SR 软驱阈值       | SR 电压上升                 |     | -70  |     | mV  |  |

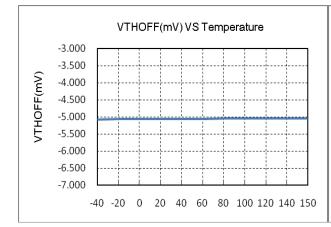

| V <sub>THOFF</sub>   | SR 关断阈值       | SR 电压上升                 |     | -5   |     | mV  |  |

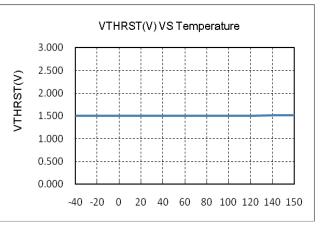

| V <sub>THRST</sub>   | SR 重置阈值       | SR 电压上升                 |     | 1.5  |     | V   |  |

| 内部 GD 部分             | -             |                         |     |      | •   |     |  |

| Rgd_up               | GATE 上拉电<br>阻 |                         |     | 3    |     | Ω   |  |

| Rgd_down             | GATE 下拉电<br>阻 |                         |     | 1.2  |     | Ω   |  |

| F_MAX                | 最大工作频率        |                         | 70  |      |     | kHz |  |

| T <sub>DON</sub>     | 导通延时          | SR 触发到 GD 电压上升到 4V      |     | 85   |     | ns  |  |

| T <sub>DOFF</sub>    | 关断延时          | SR 触发到 GD 电压下降到 1V      |     | 45   |     | ns  |  |

| T <sub>GDR</sub>     | 上升沿时间         | GD 电压 1V 到 4V, CL=6.3nF |     | 70   |     | ns  |  |

| T <sub>GDF</sub>     | 下降沿时间         | GD 电压 4V 到 1V, CL=6.3nF |     | 40   |     | ns  |  |

| MOS 部分               |               |                         |     |      |     |     |  |

| R <sub>DS(ON)</sub>  | 导通电阻          | VCC=5V                  |     | 13   |     | mΩ  |  |

## 十一、典型特性曲线

## 十二、典型应用

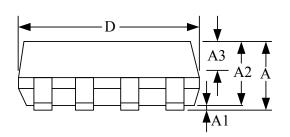

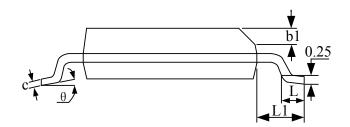

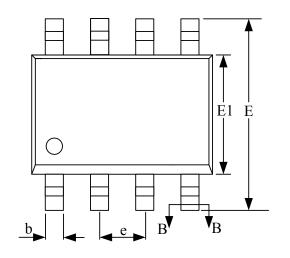

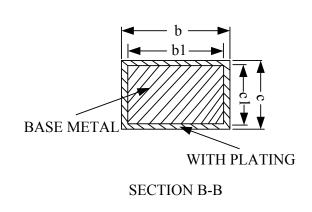

# 十三、封装外形 单位: (mm)

## SOP8

| SYMBOL   | MILLIMETER |      |      | SYMBOL   | MILLIMETER     |     |      |  |

|----------|------------|------|------|----------|----------------|-----|------|--|

| STIVIBOL | MIN        | NOM  | MAX  | STIVIBOL | MIN            | NOM | MAX  |  |

| А        | _          | -    | 1.75 | D        | 4.70 4.90 5.10 |     |      |  |

| A1       | 0.05       | -    | 0.15 | E        | 5.80 6.00 6.2  |     |      |  |

| A2       | 1.30       | 1.40 | 1.50 | E1       | 3.70 3.90 4.1  |     | 4.10 |  |

| A3       | 0.60       | 0.65 | 0.70 | е        | 1.27BSC        |     |      |  |

| b        | 0.39       | _    | 0.48 | h        | 0.25 — 0.5     |     | 0.50 |  |

| b1       | 0.38       | 0.41 | 0.43 | L        | 0.50 — 0.8     |     | 0.80 |  |

| С        | 0.21       | _    | 0.26 | L1       | 1.05BSC        |     |      |  |

| c1       | 0.19       | 0.20 | 0.21 | θ        | 0 — 8°         |     | 8°   |  |

## 十四、使用附件

#### ◆ 功能概述

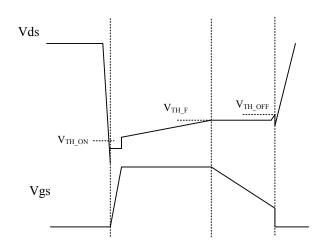

SP6552FL 检测内部 MOSFET 的漏源电压。当 Drain 端电压低于开启阈值( $V_{THON}$ ),驱动脚 GATE 输出高电平,内部 MOSFET 打开,电流从原来的体二极管转换为 MOSFET 的导电沟道,该过程将降低导通损耗。流经 MOSFET 的电流线性减小的过程中,源漏两端的电压  $V_{gs}$  同步降低。当电压低至软驱阈值( $V_{THOFF}$ )), $V_{gs}$  电压下降到维持  $V_{ds}$  一直处于软驱阈值的电压点。当  $V_{gs}$  电压超过关断阈值( $V_{THOFF}$ ),SP6552FL 将内部 MOSFET 的 GATE 下拉到 0V。见图 1。

图 1 SP6552FL 的典型波形

#### ◆ 供电

芯片供电电压由内部电路检测。当 VCC 脚电位低于关断电压阈值后,芯片停止工作。为了防止噪声干扰,建议连接一个陶瓷电容到 VCC 脚和 GND 脚之间,电容应尽量靠近 VCC 脚。VCC 脚内部被钳位到 6V。

#### ◆ UVLO 模式

当 VCC 电压超过开启电压  $V_{CC_{ON}}$ ,芯片退出欠压锁存(UVLO)模式。当 SP6552FL 的 VCC 脚电压维持在欠压状态时,GATE 脚驱动电路保持关断,芯片维持在较低的静态电流。

#### ◆ 最小导通时间

当内部 MOSFET 打开时,将产生振铃。最小导通时间屏蔽  $V_{THOFF}$  比较器来保持内部 MOSFET 打开,,持续时间至少维持一个最小导通时间。若在最小导通时间之前达到关断阈值电压  $V_{THOFF}$ ,MOSFET 将保持开启直到最小导通时间结束。

#### ◆ DRAIN 端电压内部检测

DRAIN 端连接内部控制器的电压阈值比较器,当 DRAIN 端电压低于-200mV 阈值后,内部比较器开启 MOSFET 的栅极驱动电压,MOSFET 开启,导通后,内部比较器继续侦测 DRAIN 到 GND 的电压,当电压超过-5mV 后,内部比较器翻转,关闭 MOSFET 的栅极驱动电压。在 MOSFET 关断后,DRAIN 端将承受较高的脉冲振铃电压,芯片的高压工艺可以确保芯片正常工作。

#### ◆ 正常工作模式

当 VCC 电压超过开启电压  $V_{CC\_ON}$ 后,SP6552FL 开始正常工作。芯片从欠压模式进入正常工作模式后,GATE 脚保持输出低电平,当  $V_{SR}$  超过  $V_{THRST}$ ,GATE 脚变为高电平。该过程确保了 GATE 脚在开关周期过程中不会被使能。一旦开启,GATE 脚将持续驱动内部 MOSFET。逐周期最小导通时间保护电路在正常工作模式下将被使能。

#### ◆ 最小导通时间(MOT)保护模式

如果次级电流导通的时间小于最小导通时间,下一次开关将被抑制。这项功能可以避免当输入电压很低或者极轻载/空载情况下的反向恢复电流并且通过关断 GATE 输出来减小待机功耗。在正常工作模式下,逐周期最小导通时间检测电路持续工作,因此,当负载增加到一定程度使得次级导通时间大于最小导通时间时,芯片可以自动重新进入正常工作模式。

#### ◆ 导通阶段

当内部电流首先流经 MOSFET 的体二极管,会产生一个负的 VDS 压降。体二极管的压降远大于内部 MOSFET 的导通电阻产生的压降因此可以触发导通阈值  $V_{THON}$ 。此时,SP6552FL 将驱动内部 MOSFET 使其导通,电流流经导通电阻降低 VDS 电压。电流切换过程中会伴随着一些振铃,有可能会触发内部比较 器产生关断信号,因此,最小导通屏蔽时间被用来维持 MOSFET 导通一小段时间直到振铃结束。

#### ◆ 断续模式 (DCM) /准谐振模式(QR)关断阶段

芯片内部 MOSFET 打开后,直到电流下降到关断阈值  $V_{THOFF}$  之前都不会关断。不同的工作模式下情况会不一样。在断续模式下,电流以一个相对小的 dI/dt 穿过关断阈值。一旦达到关断阈值,SP6552FL 将关断 GATE 使得电流再次流经体二极管,VDS 电压跳变到一个较大的负值。由于有残余电流,VDS 电压很有可能会重新触发导通阈值  $V_{THON}$ ,所以在  $V_{THOFF}$  被触发后, $V_{THON}$ 需要有一段屏蔽时间( $T_{BLANK}$ )才可以被重新触发。屏蔽时间由电路内部设置。VDS 需要达到一个正的电压  $V_{THRST}$  来结束屏蔽过程,然后芯片准备开启下一个周期。

#### 声明:

- 1、无锡硅动力微电子股份有限公司保留 DATA SHEET 的更改权, 恕不另外通知。客户在下单前应获取最新版本资料, 并验证相关信息是否完整和最新。

- 2、任何半导体产品在特定条件下都有一定的失效或发生故障的可能,买方有责任在使用本公司产品进行系统设计和整机制造时遵守安全标准并采取安全措施,以避免潜在失败风险可能造成人身伤害或财产损失情况的发生。

- 3、产品提升永无止境,我公司将竭诚为客户提供更优秀的产品。